На фона на нарастващото търсене от AI, високопроизводителни изчисления (HPC) и центрове за данни, високоскоростните връзки стават критични за производителността на чиповете. Niuxin Semiconductor наскоро обяви, че е завършил пълно PCIe IP портфолио, обхващащо PCIe 3.0 до PCIe 5.0, с внедрявания в множество проекти на производители на чипове, някои от които са достигнали валидиране на лента.

Неговият PCIe 5.0 IP поддържа скорости на данни до 32 GT/s и е завършил силициева валидация по 12nm процес, с приложения в AI изчислителни възли, карти за ускоряване на данни и SSD контролери от висок клас. PCIe 4.0 IP е валидиран в 28nm, 22nm и 12nm възли и навлиза в подготовка за масово производство. За зрелите пазари, PCIe 3.0 IP вече е постигнал масово производство при 22nm и 40nm, обслужвайки центрове за данни, индустриални и потребителски електронни приложения.

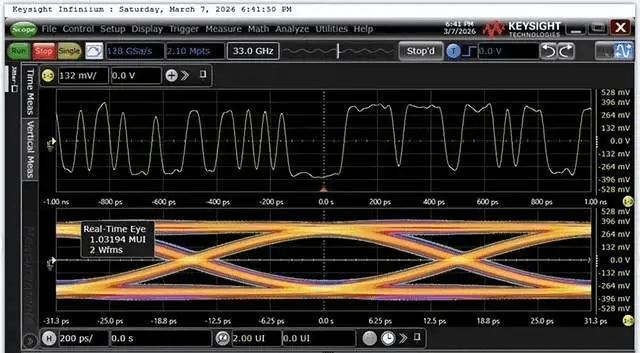

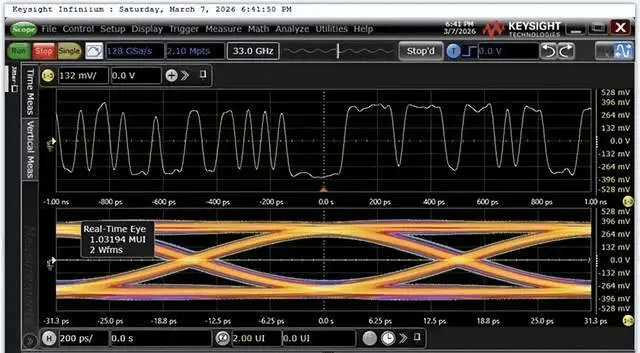

Технически, компанията подобрява целостта на сигнала чрез вериги за възстановяване на тактови данни (CDR) и техники за изравняване като FFE и DFE, постигайки стандартни за индустрията проценти на битови грешки, като същевременно поддържа многоканални конфигурации и дизайн с ниска мощност. Неговите IP решения също са съвместими между поколенията PCIe, улеснявайки системната интеграция.

Компанията добави, че разработката на PCIe 6.0 IP е завършена и напредва към търговско внедряване, с продължаващ фокус върху високоскоростните интерфейси и оптимизацията на системно ниво.

Източник: JAZZYEAR

Source link

Like this:

Like Loading…

Нашия източник е Българо-Китайска Търговско-промишлена палaта